芯片为大数据和人工智能的发展提供源源不断的动力,芯片速度的提升得益于晶体管的微缩,然而当前传统硅基场效应晶体管的性能逐渐接近其本征物理极限。国际半导体器件与系统路线图(The International Roadmap for Devices and Systems, IRDS)预测硅基晶体管的极限栅长将停止在12 nm,工作电压不能小于0.6 V,这定义了未来硅基芯片缩放过程结束时的最终集成度和功耗,因此亟需发展新型沟道材料来延续摩尔定律。原子级厚度的二维半导体因其超薄体和高迁移率的优势,作为未来芯片沟道材料的有力候选者之一,吸引了科学界和工业界的广泛兴趣。近年来英特尔、台积电、三星和欧洲微电子中心等全球领先半导体制造公司与研究机构均对二维材料投入研究。然而受限于接触、栅介质和材料等方面的瓶颈,迄今为止所有二维晶体管所实现的性能均不能媲美业界先进硅基晶体管,其实验结果远落后于理论预测,不足以展示二维半导体的最终潜力。

近期,北京大学电子学院彭练矛教授-邱晨光研究员课题组制备了10纳米超短沟道弹道二维硒化铟晶体管,首次使得二维晶体管实际性能超过Intel商用10纳米节点的硅基Fin晶体管,并且将二维晶体管的工作电压降到0.5 V,这也是世界上迄今速度最快能耗最低的二维半导体晶体管。相关研究成果以“Ballistic two-dimensional InSe transistors”为题,2023年3月22日在线发表于《自然》(Nature,网页链接:https://www.nature.com/articles/s41586-023-05819-w#citeas)。电子学院博士生姜建峰与徐琳博士为并列第一作者,彭练矛教授和邱晨光研究员为共同通讯作者,北京大学电子学院为论文唯一单位。

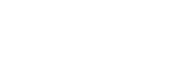

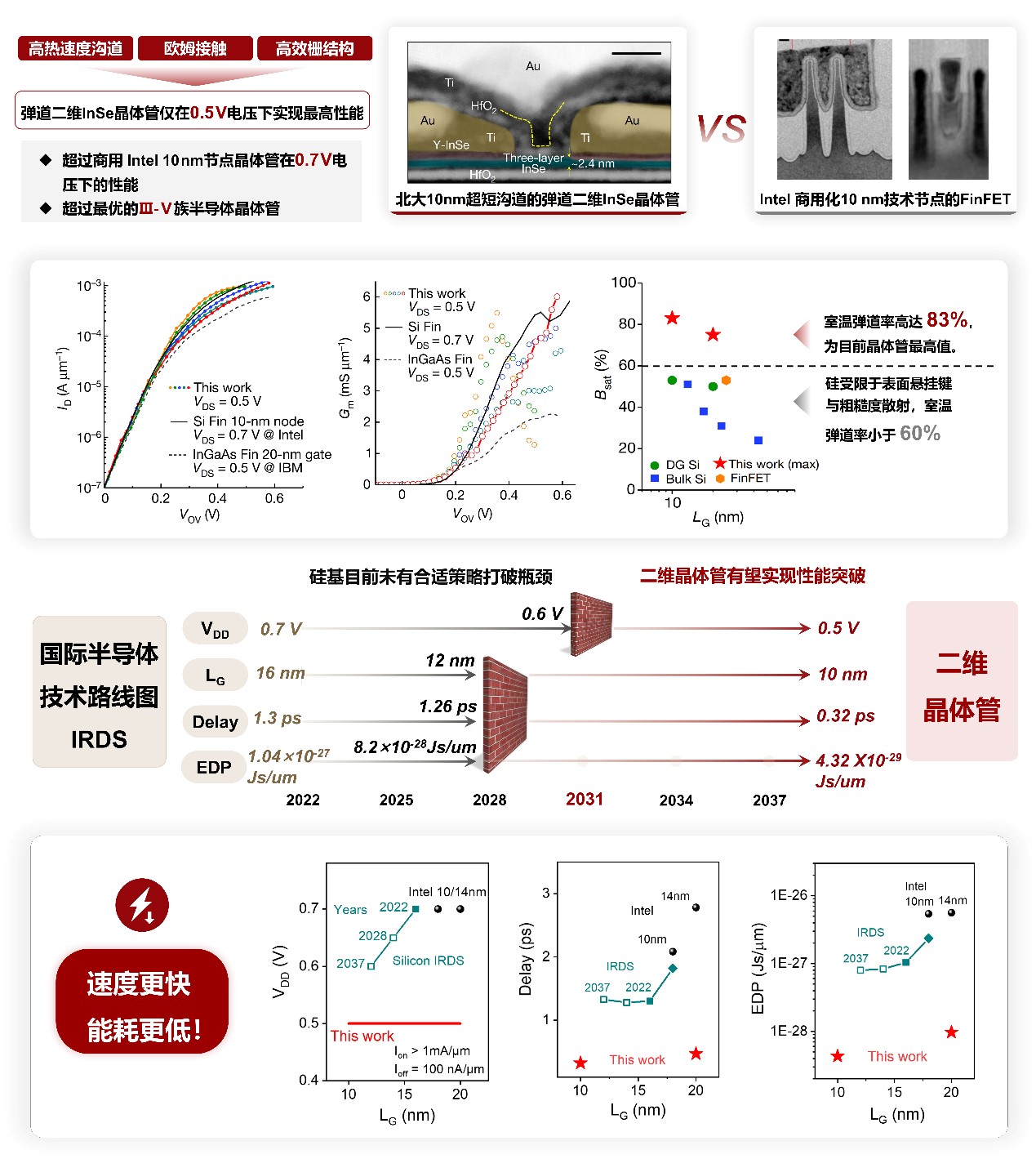

本工作实现了三方面技术革新:采用高载流子热速度(更小有效质量)的三层硒化铟作沟道,实现了室温弹道率高达83%,为目前场效应晶体管的最高值,远高于硅基晶体管的弹道率(小于60%);解决了二维材料表面生长超薄氧化层的难题,制备出2.6纳米超薄双栅氧化铪,将器件跨导提升到6毫西•微米,超过所有二维器件一个数量级;开创了掺杂诱导二维相变技术克服了二维器件领域金半接触的国际难题,将总电阻刷新至124欧姆•微米,满足集成电路未来节点对晶体管电阻的要求(220欧姆•微米)。

对标业界IRDS所预测的硅基器件发展路线图,北大团队所实现的弹道二维硒化铟晶体管打破了四个硅基终极“红墙”:1)沟长缩小到10纳米(超越硅基极限12纳米),同时保持理想的亚阈值摆幅75毫伏量程,DIBL仅20毫伏/伏,该器件关态特性超过硅基最优FinFET技术。2)电压缩小到0.5伏 (超越2031年硅基极限0.6伏),将器件电流从100纳安/微米标准关态打开到超过1毫安/微米开态。3)门延时缩减到0.32皮秒,四倍优势于硅基极限1.26皮秒。4)功耗延迟积缩减到4.32E-29焦秒/微米,比硅基极限低一个量级。

这项工作突破了长期以来阻碍二维电子学发展的关键科学瓶颈,将n型二维半导体晶体管的性能首次推近理论极限,率先在实验上证明出二维器件性能和功耗上优于先进硅基技术,为推动二维半导体技术的发展注入强有力的信心和活力。

图1 Nature官网论文截图

图2 弹道二维硒化铟晶体管与先进节点硅基晶体管的比较

图3 器件开关态特性

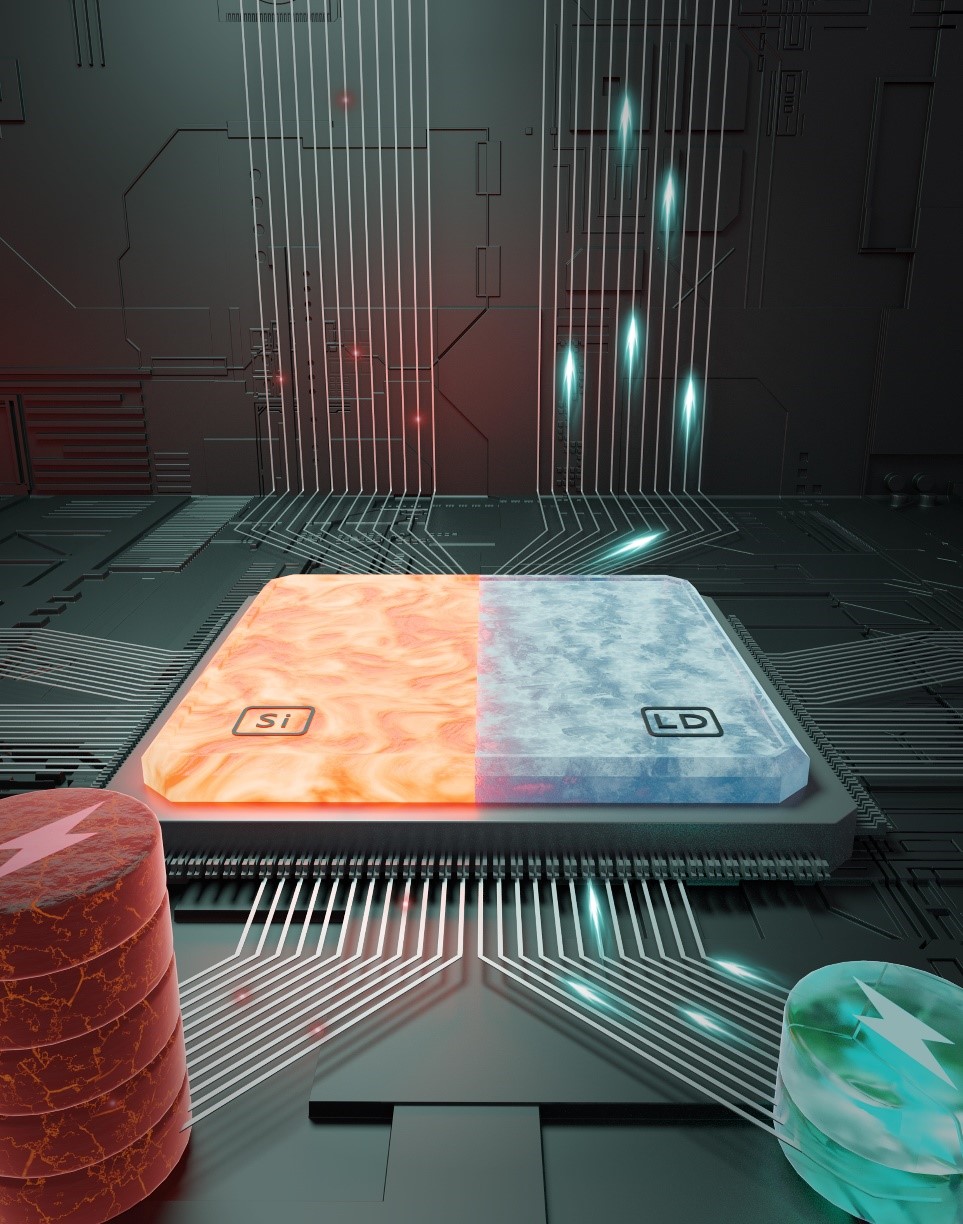

图4 展望:更快更省电的低维半导体芯片