2024年9月27日下午,北京大学电子学院前沿论坛第70期讲座成功举办。本次讲座邀请了芯动微电子科技(北京)有限公司制程整合和商务拓展副总罗彤先生。罗总为大家分享了题为“数据和算力—集成电路产业未来的趋势和边界”的精彩报告。本次报告由电子学院陈清教授主持,70多名师生参与了本次讲座。

讲座开始,罗彤副总从广义的摩尔定律讲起,认为文字承托着知识,而有了文字这个存储知识的媒介,知识呈指数型增长并在近现代达到爆炸式增长阶段。知识总量的爆炸式增长催生了人类社会的生产力和人口的增长,使社会从原始进步到目前的高现代化水平。

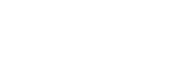

然后,罗彤副总从经济学的供应和需求的角度为大家梳理了集成电路产业数十年来的发展路径。罗彤副总指出,需求并非来源于社会中的个体,而是来源于“计算”、“传输”、“存储”等数据需求。在集成电路产业发展初期,伴随着计算机科学的缓慢发展速度,上述数据需求能够很好地被芯片的微缩(Scaling down)所满足,即微缩和生产的工艺技术及电路结构等优化能够“供应”数据的需求。然而,随着计算机科学等学科的发展,尤其是近年来基于大语言模型的AI发展,数据量不断上升且计算速度要求不断提高,芯片的微缩不能够完全“供应”这些需求,导致集成电路产业遇到了“边界”。存储产品和数据需求之间供不应求的关系是未来电子领域的一大瓶颈。

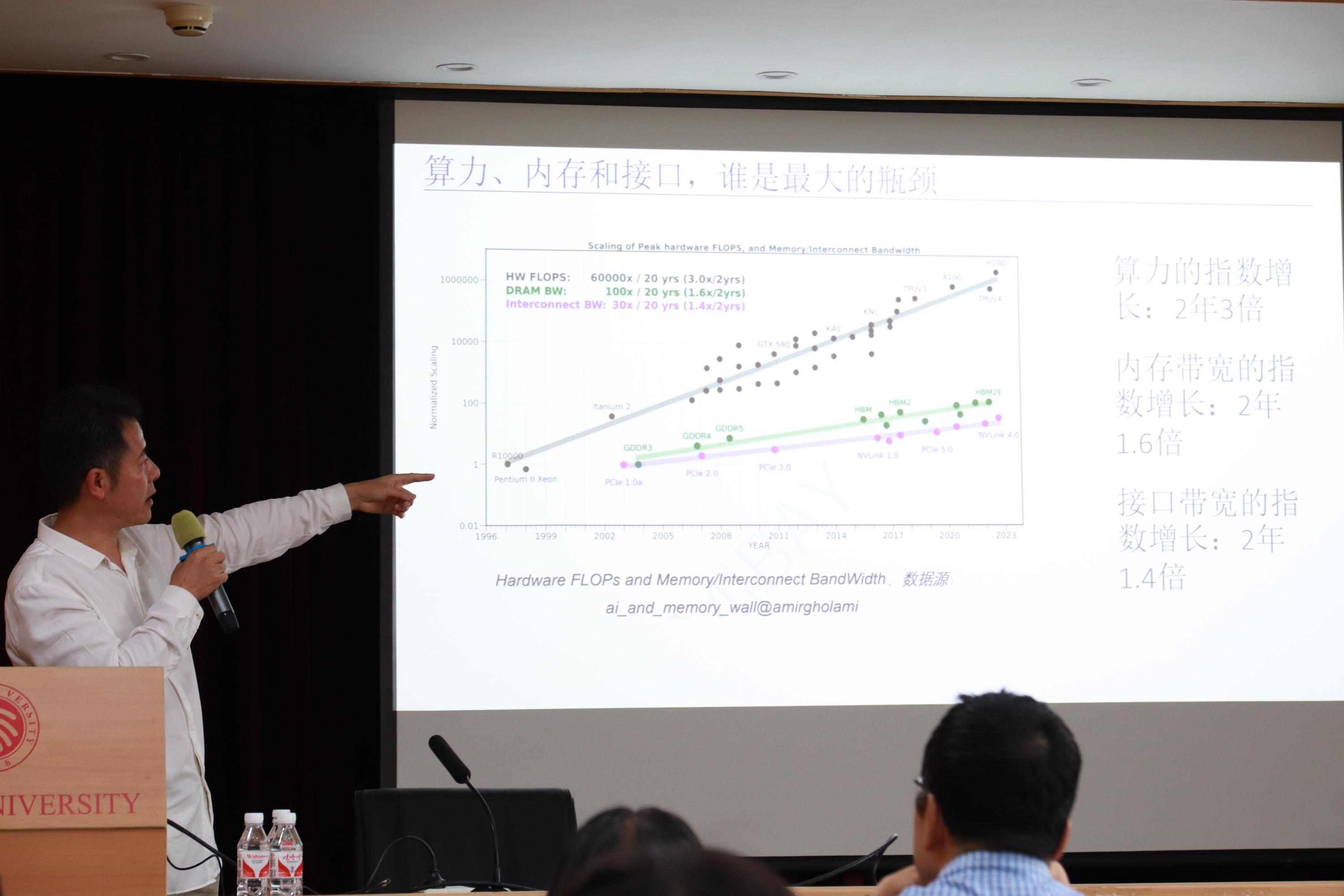

罗彤副总从冯·诺依曼架构来剖析行业发展瓶颈。首先,罗彤副总认为“接口”作为数据传输交换的道路是目前最大瓶颈,这个瓶颈可以通过独立I/O接口芯片等缓解压力。其次,算力单元的碎片化和单元化与摩尔定律描述的scaling down息息相关,因此也会遇到算力上限。存储(Memory)的瓶颈是目前计算发展的最大限制。随着目前AI的发展,GPU等并行计算单元需要单次高速地吞吐较大信息量,以通过训练方式提升模型准确度和能力,因此要求DRAM具有高带宽、大的容量和快的速度。在前数十年,DRAM产业还能通过单元器件尺寸微缩以遵循摩尔定律的方式降低成本。然而,存储器件因为电容本身尺寸的物理限制而无法提供更高密度的数据存储和更高效率的数据传输能力,导致算力遇到边界。罗彤副总提出,解决上述问题的集成方法有继续光刻scaling down和先进封装等方法。其中,继续光刻scaling down会因为尺寸的物理极限和良率控制问题而投入较大成本。因此,在面对狭义摩尔定律所描述的器件尺寸微缩遇到边界时,另辟蹊径诉诸于封装(package)能够为芯片行业开辟一条新的发展路径。先进封装,如系统级封装(System in Package)、芯粒(Chiplet)封装、2.5D和3D堆叠、Wafer-on-wafer替代HBM堆叠等,为数据传输和存储提供了更高效率,以满足AIGC对未来存储器要求。

在互动环节,现场老师和同学们踊跃提问,罗总逐一解答。当谈到未来计算模式时,罗总指出未来算力系统将回归集中以应对芯片成本和算力能耗的急剧增长。当讨论到类脑计算和神经形态计算时,罗总认为这类新架构芯片在理论上具有显著先进性,而其应用和发展取决于目前计算科学具体专用领域的发展。最后,罗总寄语希望我们能够透过广义和狭义的摩尔定律看到本质,能够在未来科研和工作道路上长久稳定地进步发展,共同努力实现更大突破。报告结束时,电子学院陈清教授为罗总颁发了北京大学电子学院前沿论坛纪念牌,并合影留念。